等長主要是讓SI特性好,多個訊號線一定有共模和差模的部分,但共模傳輸的方式易受噪音干擾,所以在高速介面上(例如Flash/RAM/USB/PCIE等等)都是使用差模方式來做傳輸,即差分訊號輸入,經過走線最後在端點的差分放大器放大,因為差分放大器會將共模的地方疊加並消除,所以加在其上的共同噪音也跟著消除了,因此剩下差模的成分被放大成為有效訊號在給另一端裝置/外設做處理,這就是整個脈絡

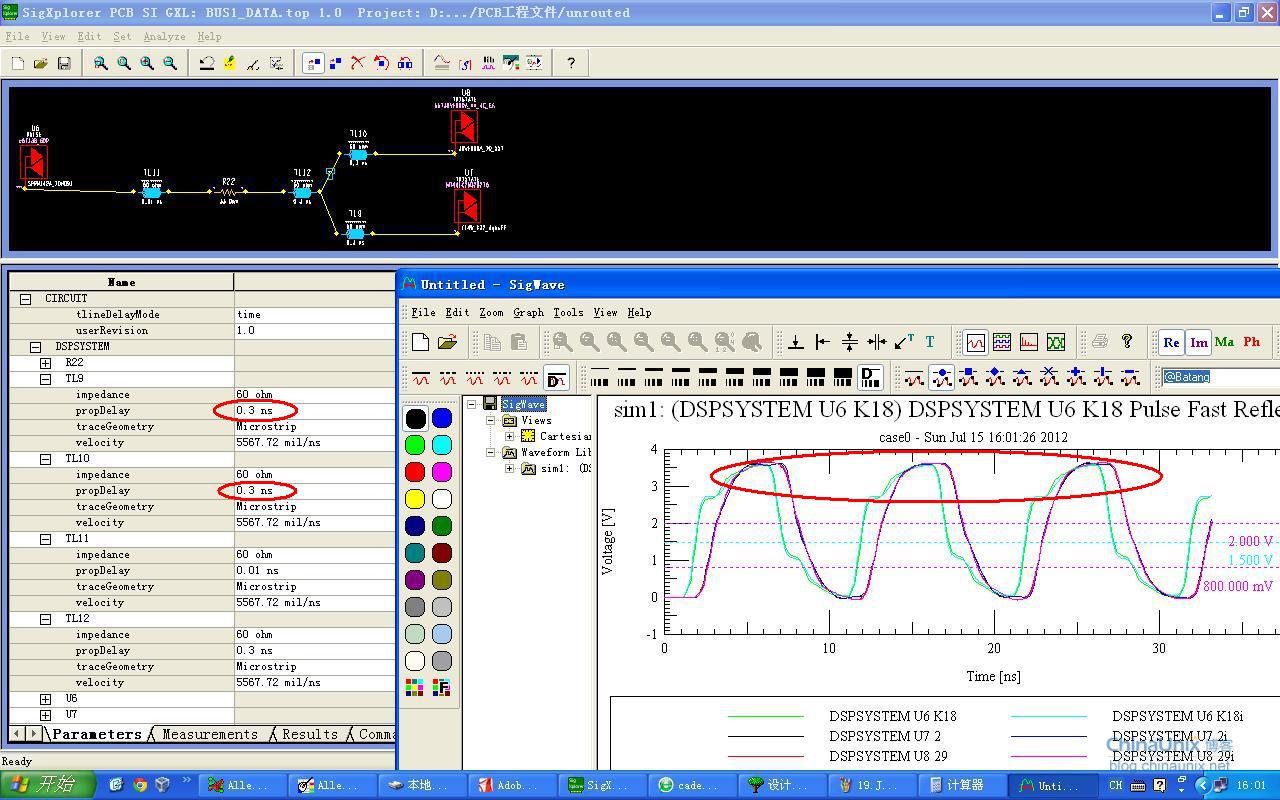

所以回過頭講等長這個議題時候,基礎理論在於電磁學的阻抗匹配,實務上我們無法每條走線都詳細計算阻抗,現實干擾因素很多,因此EDA工具多半幫你做模型化後的估計並分析,在Cadence中就是SI了,訊號越完整代表訊號正確無誤,更加可靠,可參考下面這篇文章不錯

http://archive.ednchina.com/bbs.ednchina.com/BLOG_ARTICLE_3010632.HTM

以上供參考