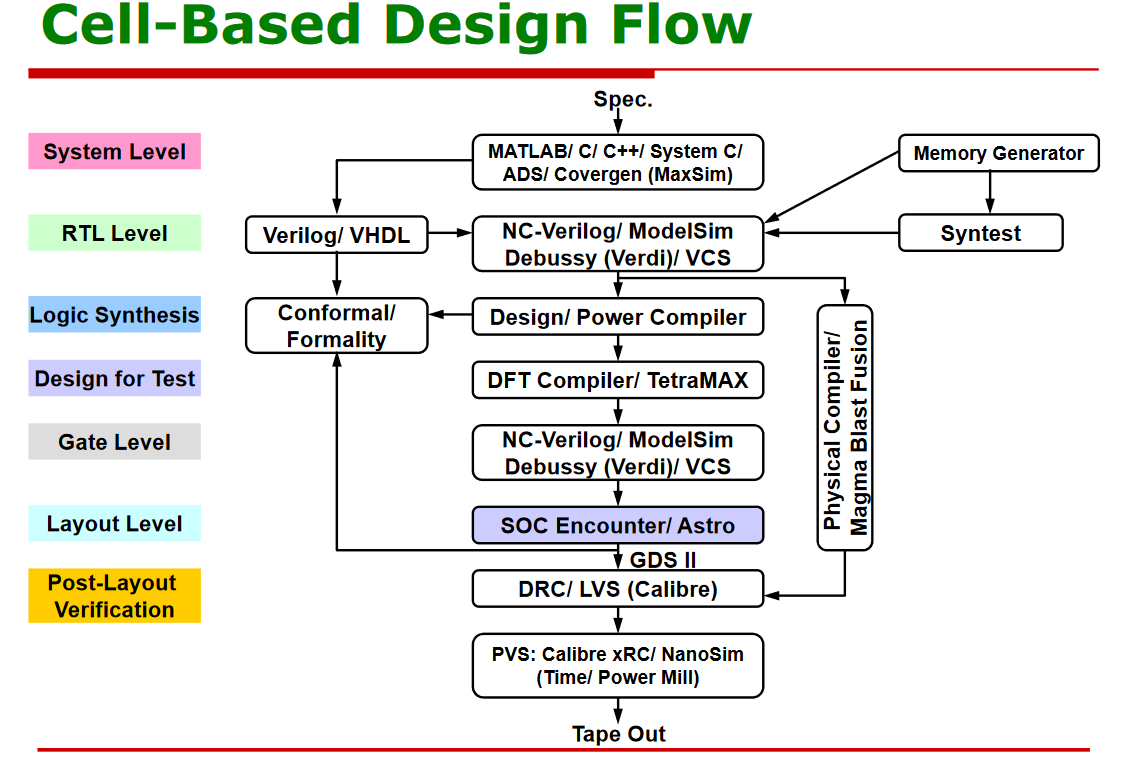

我們的Flow如下,其中C家和S家各自有對應的EDA Tool可替換

1. 初期RTL設計- XCode

2. 初期RTL模擬- Cadence NC-Verilog

3. 中期RTL Synthesis - Synopsys Design compiler

4. 中期Gate Level驗證 - Synopsys DFT compiler

5. 中期Gate Level測試- Synopsys DFT compiler

6. 中期Gate Level模擬- Cadence NC-Verilog

7. 後期Layout之Floorplan - SOC Encounter

8. 後期Layout之Placement - SOC Encounter

9. 後期Layout之Clock Tree Synthesis - SOC Encounter

10. 後期Layout之Power Ring - SOC Encounter

11. 後期Layout之Route - SOC Encounter

12. 後期Layout之Pin assignment - SOC Encounter

13. 後期Layout之DRC/LVS - SOC Encounter

14. 後期Layout之產生GDS檔案 - SOC Encounter

15. Tape out

其中步驟7~13會進行多次的Timing check (WNS),以達到規格

以上供您參考