基于UCD92xx与UCD7xxx的非隔离数字电源,其输出电压在软启动阶段经常出现“台阶”现象,波形不平滑,尤其是输出电压设定为较低值时,如 1.0V。这种“台阶”现象与UCD92xx软启动的设计原理有关,但完全可以通过一定的措施来优化并最终解决。本文从UCD92xx的环路和最小占空比 宽度两个方向进行优化与分析,最终取得了理想的效果。

1、软启动原理及待优化输出电压波形

数字电源UCD92xx的软启动是通过对参考电压以步进方式增加来实现的,整个过程是由芯片内部的软件自动完成的。在一款基于UCD9224和UCD74120的单板上测试时发现,其输出电压波形在软启动阶段有明显的“台阶”现象,波形不平滑。

1.1 数字电源软启动原理介绍

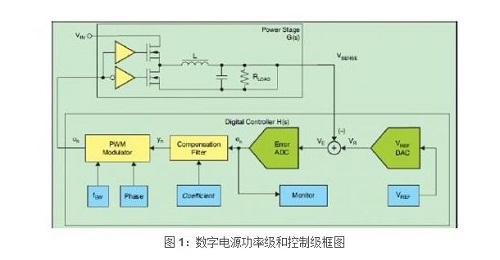

图1所示的是数字电源UCD92xx的功率支路和控制支路。控制支路主要集成在UCD92xx芯片内部,包含误差生成及模数转换,环路补偿,PWM计算及产生等。其中,参考电压(VREF)电压的设置亦包含在控制支路。

依据软件算法,在软启动阶段,VREF每100us增加一次,直至软启动完成,即输出电压达到最终的设定值。例如,输出电压设定为1.0V,软启动的时间设置为4ms,则在软启动阶段输出电压每一次增加25mv,直至达到1.0V。

1.2 待优化的输出电压波形

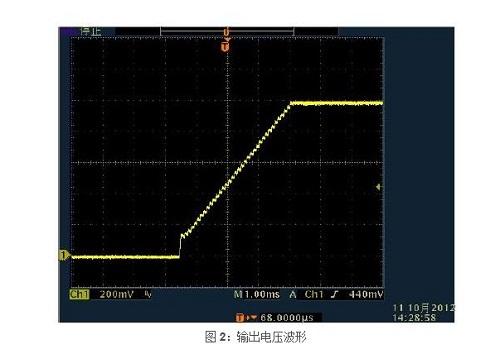

图2所示的是输出电压波形,可以观察到在软启动阶段输出电压的波形不够平滑,有明显的“台阶”现象。该波形是在一款基于UCD9224和UCD74120

的参考版上测得。主要测试条件为:测试环境常温,输入电压为12V,输出电压为1.0V,输出端带载20A。另外,测试时,数字环路的详细配置见下文

2.4节。

1.3 输出电压“台阶”现象的初步分析

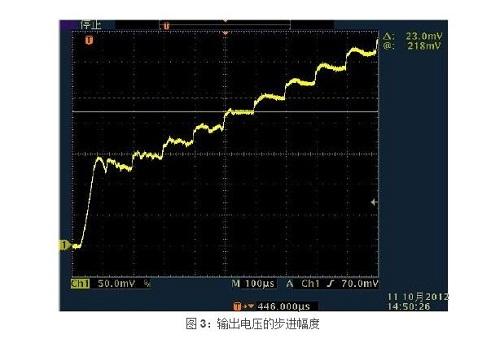

图3所示的是时间轴展开后观察到的输出电压波形。通过测量可知,每经过100us输出电压增加一次,增加的幅度大约为23mV,与理论计算值25mV基本一致。

同时也可以观察到,输出电压的每一次增加都是很快的完成,而不是缓慢增加。从功率级支路上分析,这是由于占空比快速增加造成。从控制级支路分析,则原因可以初步归结为环路过快造成的。

2 数字电源模拟前端及环路

数字电源控制环路包含了模拟前端,数字环路补偿等模块,在配置环路时需要综合考虑。其中,数字环路还包含非线性增益模块,使能后可以有效提升整个电源的动态响应性能。

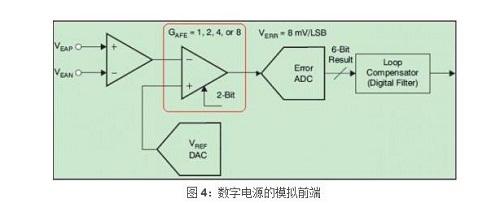

2.1 数字电源模拟前端(AFE)

图4红色框内电路为数字电源模拟前端(Analog-FrontEnd,AFE)的一部分,其增益可以设置为1,2,4,8等四个不同的值。设置不同的增益,则ADC的输出精度也随之不同,比如设置增益为4,则输出精度为2mV;设置增益为1,则输出精度为8mV。

在相同输入误差(VEAP-VEAN)的情况下,不同的AFE增益值将直接影响环路指标。其影响趋势为,增益越大,环路带宽越宽。

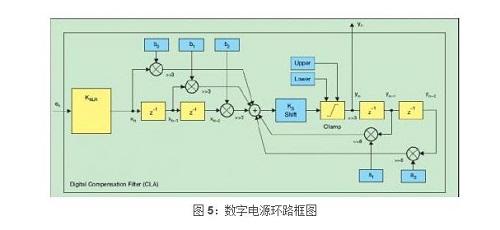

2.2 数字电源环路

图5所示的是数字电源的环路框图。其中,是误差放大器的输出,为数字信号;是环路的输出,亦为数字信号,输入到PWM模块。模块是非线性增益模块,可以使

能或禁止,下一节会进行详细分析。a1,a2,b0,b1,b2是环路补偿的系数,允许用户修改以适应不同的功率级设计。需要说明的是,UCD92xx内

部设计有2套a1~b2的参数,分别用于软启动阶段和正常运行阶段。

2.3 非线性增益

图5中的模块即为非线性增益模块,其详细的框图如图6。当en不超过lim0时,增益为Gin0;当en超过Lim0但不超过lim1时,增益为

Gain1;依此类推。非线性增益模块依据误差放大器的输出进行不同程度的放大,可以有效的提升动态响应性能。如果Gain0设置为1,即便使能非线性增

益模块,也不会影响环路指标。如果Gain0由1修改为0.75或1.25,则会影响环路指标。其影响趋势为,增益越大,环路带宽越宽。

2.4 数字电源环路配置

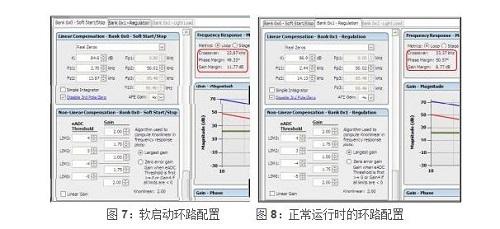

图6和图7是使用数字电源开发工具Fusion Digital Power Designer来配置环路的软件截图。该工具可以模拟整个环路并给出配置之后的闭环环路指标,包括截止频率,相位余度和增益余度,极大的方便了环路的调试和优化。

图6所示的是软启动时的环路配置。零极点的信息在“Linear

Compensation”方框中,其中AFE的Gain设置为4×;该配置中使能了非线性增益,其Limit值和Gain值是允许用户修改的。最终,整

个环路的指标为23.87KHz(截止频率),49.33°(相位余度),11.77dB(增益余度)。

图7所示的是正常运行时的环路配置。零极点的信息在“Linear

Compensation”方框中,其中AFE的Gain为4×;该配置中使能了非线性增益,其Limit值和Gain值是允许用户修改的。最终,整个环

路的指标为33.7KHz(截止频率),50.57°(相位余度),8.77dB(增益余度)。

正是采样上述配置,输出电压在软启动阶段其波形有明显的“台阶状”。下面将尝试放慢环路后,验证是否可以优化软启动阶段的波形。

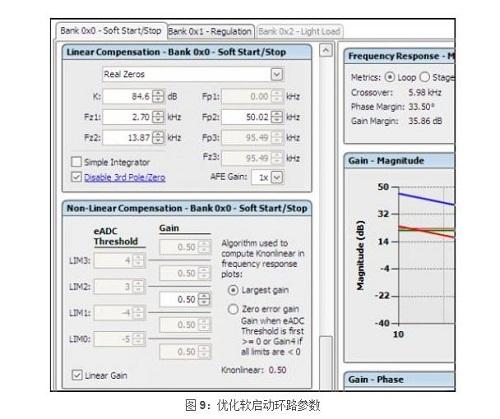

2.5 优化环路配置

图9是软启动环路优化后的软件截图。环路的优化包括:

1)不再使能非线性增益,同时将Gain0由1修改为0.5;这可以降低环路的低频增益,最终降低环路带宽;

2)将AFE的Gain由4修改为1,同样可以降低环路带宽。1倍的Gain将使AFE的输出的精度变差,并最终影响到输出电压,但考虑到软启动阶段对输 出电压的精度要求略低,因此可以上述修改可以接受。需要说明的是,为保证正常运行时输出电压的性能(精度,动态性能等),正常运行时对应的环路参数将保持 不变。

图10所示的是优化环路后的输出电压波形,可以观察到在软启动阶段的“台阶”现象消失,波形平滑。

图11是将时间轴展开后的输出电压波形,可以观察到其步进的时间依然是100us,步进的幅度为24mV(与理论值25mV基本一致),但每一次的步进不再是突然增加,而是缓慢增加。因此,输出电压波形变得较为平滑。

但是,在图10所示的波形中可以观察到,输出电压在启动时刻有一个正向过冲并很快回落。严格意义上,该过冲会影响输出电压波形的单调性,在一些应用场景中是不运行的。下文将针对该过冲进行优化。

3 调整最小驱动时间进一步优化输出波形

优化环路后输出电压在软启动阶段变得较为平滑,但会存在一个明显的过冲,需要进行优化。下文通过调整最小占空比宽度来消除该过冲。

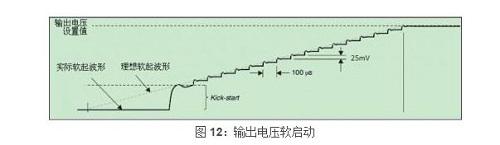

3.1 数字电源软启动的kick-start

图12中所示的是数字电源的输出电压软启动示意图。在开始时刻,输出电压有一个快速的上升,称之为“Kick-start”。Kick-start的幅度是根据下面公式计算出的:

Vstart=Vin×DRIVER_MIN_PULSE×Fsw

其中,DRIVER_MIN_PULSE是指UCD92xx发出的最小占空比的宽度,允许用户自行设定。

以图10为例,输出电压Kick-start的幅度约为185mV。其DRIVER_MIN_PULSE设置为50ns,理论计算Kickstart的幅度为:12V×50ns×300KHz=180mV。实际值与理论值基本一致。

3.2 调整最小占空比宽度

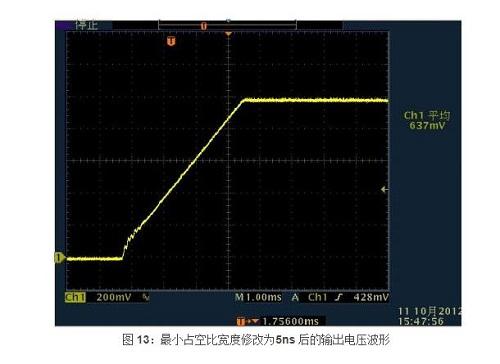

将DRIVER_MIN_PULSE由目前的50ns修改为5ns,以验证其对输出电压的过冲有无改善。图13即为输出电压波形,可以观察到过冲已经消失,但在起始时刻,输出电压不再平滑。

分析原因可知,当DRIVER_MIN_PULSE设置为5ns后,虽然UCD9224可以发出宽度为5ns的驱动脉冲,但UCD74120对最小占空比

的宽度有要求,5ns的宽度不足以使集成在UCD74120内部的buck上管导通,从而造成了输出电压上升的不平滑。

过小的DRIVER_MIN_PULSE值会使输出电压在起始时刻变得不再平滑;过大的DRIVER_MIN_PULSE的值则会带来正向过冲。因此,需要找到一个平衡点。

逐步增大DRIVER_MIN_PULSE的值,当设置为43ns时,达到了较为理想的平衡点,输出电压的波形如图14所示,输出不再有正向过程,而且在整个软启动阶段输出电压波形都比较平滑。

此时,输出电压Kick-start的幅度约为160mV。其DRIVER_MIN_PULSE为43ns,理论计算Kick-start的幅度为:12V×43ns×300KHz=154.8mV。实际值与理论值基本一致。

4 结论

通过修改AFE的增益值和禁止非线性增益等措施优化软启动对应的环路参数后,可以消除输出电压的“台阶”现象,使波形单调平滑上升。正常运行的环路参数无

需改动,保证了其较高的带宽,从而使输出电压的精度和动态响应等指标保持不变。通过优化最小占空比的宽度,可以消除在kick-start之后的正向过

程,使输出电压波形单调平滑。

综上两类优化措施,最终可以使输出电压波形在整个软启动阶段单调平滑。