本帖最后由 HelloWii 于 2016-6-15 20:51 编辑

使用GCC的命令行进行程序编译在单个文件下是比较方便的,当工程中的文件逐渐

增多,甚至变的十分庞大的时候,使用GCC命令编译就会变的力不从心。Linux中的

make工具提供了一种管理工程的功能,可以方便的进行程序的编译,对更新的文件进行

重新编译。

一个多文件的工程例子:

有一个工程共有5个源文件,在add目录中有add_int.c和add-float.c,两个文件分别

计算整形和浮点型的相加;在sub目录下有文件sub_int.c和sub_float.c,分别计算

整形和浮点型的相减;顶层目录有main.c文件负责整个程序。

工程中的代码分别存放在add/add_int.c,add/add_float.c,add/add.h,sub/sub_int.c,

sub/sub_float.c,sub/sub.h,和main.c中。

文件main.c

文件main.c的代码如下。在main()函数中调用整数、浮点的加减运算函数进行数值计算。

加操作:

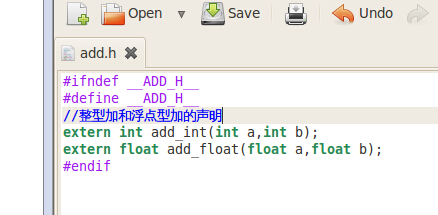

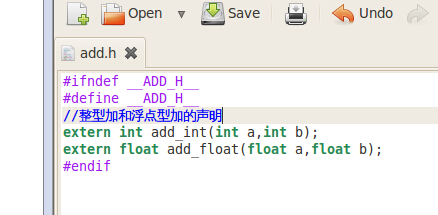

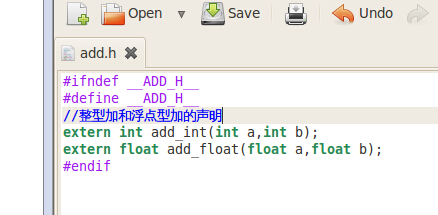

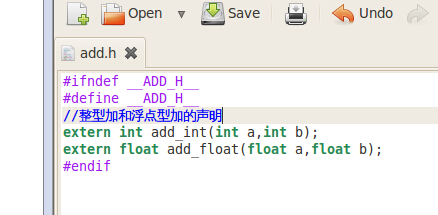

文件add.h的代码如下,包含整数和浮点数的求和函数声明。

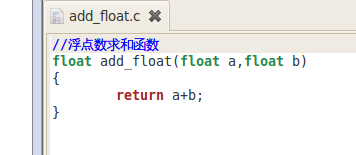

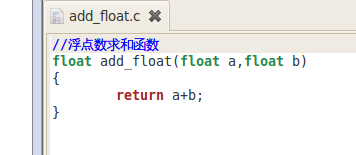

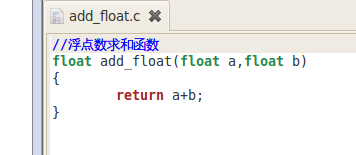

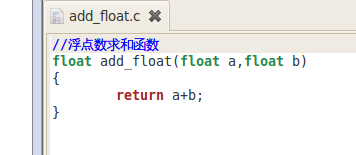

文件add_float.c的代码如下,函数add_float()进行浮点型数值的相加计算。

文件add_init.c的代码如下,函数add_int()进行整数型数值的相加计算。

减操作:

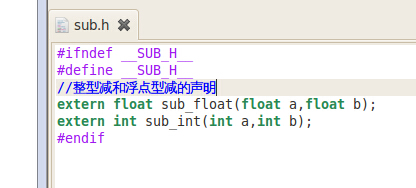

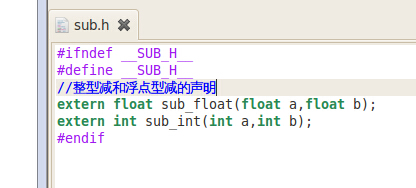

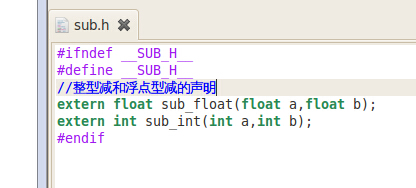

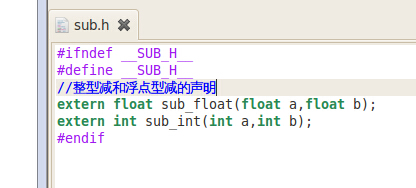

文件sub.h的代码如下,包含整数和浮点数的相减函数声明:

文件sub_int.c的代码如下,函数sub_int()进行整形的相减计算。

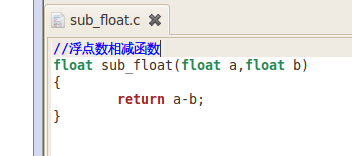

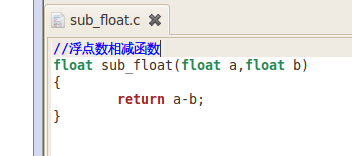

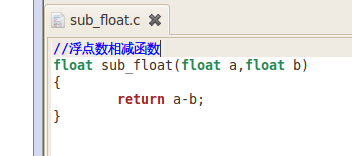

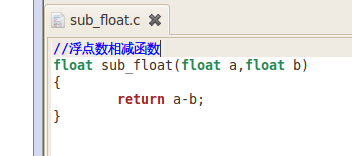

文件sub_float.c的代码如下,函数sub_float()进行浮点型的相减计算。

本帖最后由 HelloWii 于 2016-6-15 20:51 编辑

使用GCC的命令行进行程序编译在单个文件下是比较方便的,当工程中的文件逐渐

增多,甚至变的十分庞大的时候,使用GCC命令编译就会变的力不从心。Linux中的

make工具提供了一种管理工程的功能,可以方便的进行程序的编译,对更新的文件进行

重新编译。

一个多文件的工程例子:

有一个工程共有5个源文件,在add目录中有add_int.c和add-float.c,两个文件分别

计算整形和浮点型的相加;在sub目录下有文件sub_int.c和sub_float.c,分别计算

整形和浮点型的相减;顶层目录有main.c文件负责整个程序。

工程中的代码分别存放在add/add_int.c,add/add_float.c,add/add.h,sub/sub_int.c,

sub/sub_float.c,sub/sub.h,和main.c中。

文件main.c

文件main.c的代码如下。在main()函数中调用整数、浮点的加减运算函数进行数值计算。

加操作:

文件add.h的代码如下,包含整数和浮点数的求和函数声明。

文件add_float.c的代码如下,函数add_float()进行浮点型数值的相加计算。

文件add_init.c的代码如下,函数add_int()进行整数型数值的相加计算。

减操作:

文件sub.h的代码如下,包含整数和浮点数的相减函数声明:

文件sub_int.c的代码如下,函数sub_int()进行整形的相减计算。

文件sub_float.c的代码如下,函数sub_float()进行浮点型的相减计算。

加操作:

文件add.h的代码如下,包含整数和浮点数的求和函数声明。

加操作:

文件add.h的代码如下,包含整数和浮点数的求和函数声明。

文件add_float.c的代码如下,函数add_float()进行浮点型数值的相加计算。

文件add_float.c的代码如下,函数add_float()进行浮点型数值的相加计算。

文件add_init.c的代码如下,函数add_int()进行整数型数值的相加计算。

文件add_init.c的代码如下,函数add_int()进行整数型数值的相加计算。

减操作:

文件sub.h的代码如下,包含整数和浮点数的相减函数声明:

减操作:

文件sub.h的代码如下,包含整数和浮点数的相减函数声明:

文件sub_int.c的代码如下,函数sub_int()进行整形的相减计算。

文件sub_int.c的代码如下,函数sub_int()进行整形的相减计算。

文件sub_float.c的代码如下,函数sub_float()进行浮点型的相减计算。

文件sub_float.c的代码如下,函数sub_float()进行浮点型的相减计算。

加操作:

文件add.h的代码如下,包含整数和浮点数的求和函数声明。

加操作:

文件add.h的代码如下,包含整数和浮点数的求和函数声明。

文件add_float.c的代码如下,函数add_float()进行浮点型数值的相加计算。

文件add_float.c的代码如下,函数add_float()进行浮点型数值的相加计算。

文件add_init.c的代码如下,函数add_int()进行整数型数值的相加计算。

文件add_init.c的代码如下,函数add_int()进行整数型数值的相加计算。

减操作:

文件sub.h的代码如下,包含整数和浮点数的相减函数声明:

减操作:

文件sub.h的代码如下,包含整数和浮点数的相减函数声明:

文件sub_int.c的代码如下,函数sub_int()进行整形的相减计算。

文件sub_int.c的代码如下,函数sub_int()进行整形的相减计算。

文件sub_float.c的代码如下,函数sub_float()进行浮点型的相减计算。

文件sub_float.c的代码如下,函数sub_float()进行浮点型的相减计算。

生成cacu的时候,多次使用同一组.o目标文件:在cacu规则的依赖项中出现一次,

在生成cacu执行文件的时候又出现一次。直接使用文件名进行书写的方法不仅

书写起来麻烦,而且进行增加或者删除文件时容易遗忘。

Makefile中的用户自定义变量:

使用Makefile进行规则定义的时候,用户可以定义自己的变量,称为用户自定义变量。

例如,可以用变量来表示上述的文件名,定义OBJS变量表示目标文件,用CC变量

表示gcc,用CFLAGS表示编译的选项,RM表示rm -f,TARGET表示最终的生成目标

cacu。

之前冗长的Makefile可以简化成如下方式:

生成cacu的时候,多次使用同一组.o目标文件:在cacu规则的依赖项中出现一次,

在生成cacu执行文件的时候又出现一次。直接使用文件名进行书写的方法不仅

书写起来麻烦,而且进行增加或者删除文件时容易遗忘。

Makefile中的用户自定义变量:

使用Makefile进行规则定义的时候,用户可以定义自己的变量,称为用户自定义变量。

例如,可以用变量来表示上述的文件名,定义OBJS变量表示目标文件,用CC变量

表示gcc,用CFLAGS表示编译的选项,RM表示rm -f,TARGET表示最终的生成目标

cacu。

之前冗长的Makefile可以简化成如下方式:

执行命令的情况如下;

执行命令的情况如下;

make 查找到第一个执行的规则为生成cacu,但是main.o等5个文件不存在,

make按照默认的规则生成main.o等5个目标文件。

运行可执行文件:

make 查找到第一个执行的规则为生成cacu,但是main.o等5个文件不存在,

make按照默认的规则生成main.o等5个目标文件。

运行可执行文件:

执行命令的情况如下:

执行命令的情况如下:

运行可执行文件:

运行可执行文件:

重新编写后的Makefile中,生成TARGET规则的编译选项使用$@表示依赖项中的文件名称,使用$<表示目标文件的名称。

运行make命令:

重新编写后的Makefile中,生成TARGET规则的编译选项使用$@表示依赖项中的文件名称,使用$<表示目标文件的名称。

运行make命令:

运行可执行文件:

运行可执行文件:

这样,目标文件都放到了objs目录下,只有最终的执行文件cacu放在当前目录,执行

make的结果如下:

这样,目标文件都放到了objs目录下,只有最终的执行文件cacu放在当前目录,执行

make的结果如下:

编译目标文件时会自动加上路径名,并且当objs不存在时会创建此目录。

运行可执行文件:

编译目标文件时会自动加上路径名,并且当objs不存在时会创建此目录。

运行可执行文件:

在此Makefile中,不用指定OBJS的规则,make自动会按照隐含规则形成一个规则来

生成目标文件。

运行make命令:

在此Makefile中,不用指定OBJS的规则,make自动会按照隐含规则形成一个规则来

生成目标文件。

运行make命令:

运行可执行文件:

运行可执行文件:

CC编译器变量由总控Makefile统一指定,下层的Makefile直接调用即可。生成的

目标文件都放到./objs目录中,export了一个变量OBJSDIR.其中的${shelll pwd}

是执行一个shell命令pwd获得总控Makefile的当前目录。子目录Makefile的编写:

add目录下的Makefile如下:

CC编译器变量由总控Makefile统一指定,下层的Makefile直接调用即可。生成的

目标文件都放到./objs目录中,export了一个变量OBJSDIR.其中的${shelll pwd}

是执行一个shell命令pwd获得总控Makefile的当前目录。子目录Makefile的编写:

add目录下的Makefile如下:

这个Makefile很简单,编译add目录中的两个C文件,并将生成的目标文件按照总控

Makefile传入的目标文件存放路径放置。

sub目录下的Makefile与add目录下的一致,也是将生成的目标文件放到总控Makefile

指定的路径中。

这个Makefile很简单,编译add目录中的两个C文件,并将生成的目标文件按照总控

Makefile传入的目标文件存放路径放置。

sub目录下的Makefile与add目录下的一致,也是将生成的目标文件放到总控Makefile

指定的路径中。

运行make命令:

运行make命令: 运行可执行文件:

运行可执行文件:

编译程序,输出结果如下:

编译程序,输出结果如下:

运行可执行文件:

运行可执行文件:

多文件的编译:

编译多文件的项目,在上面Makefile文件编写完毕后,运行make命令:

多文件的编译:

编译多文件的项目,在上面Makefile文件编写完毕后,运行make命令:

运行结果也出来了

运行结果也出来了